ការរចនានៃហ្វូតូនិកសៀគ្វីរួមបញ្ចូលគ្នា

សៀគ្វីរួមបញ្ចូលគ្នាហ្វូតូនិក(PIC) ជារឿយៗត្រូវបានរចនាឡើងដោយមានជំនួយពីស្គ្រីបគណិតវិទ្យាដោយសារតែសារៈសំខាន់នៃប្រវែងផ្លូវនៅក្នុងឧបករណ៍ interferometers ឬកម្មវិធីផ្សេងទៀតដែលងាយនឹងរងផលប៉ះពាល់ដោយប្រវែងផ្លូវ។PICត្រូវបានផលិតឡើងដោយការបង្កើតស្រទាប់ច្រើន (ជាធម្មតា 10 ទៅ 30) នៅលើបន្ទះ wafer ដែលផ្សំឡើងពីរាងពហុកោណជាច្រើន ដែលជារឿយៗត្រូវបានតំណាងជាទម្រង់ GDSII។ មុនពេលផ្ញើឯកសារទៅក្រុមហ៊ុនផលិត photomask វាជាការចង់បានយ៉ាងខ្លាំងក្នុងការអាចក្លែងធ្វើ PIC ដើម្បីផ្ទៀងផ្ទាត់ភាពត្រឹមត្រូវនៃការរចនា។ ការក្លែងធ្វើត្រូវបានបែងចែកជាច្រើនកម្រិត៖ កម្រិតទាបបំផុតគឺការក្លែងធ្វើអេឡិចត្រូម៉ាញ៉េទិចបីវិមាត្រ (EM) ដែលការក្លែងធ្វើត្រូវបានអនុវត្តនៅកម្រិតរលករង ទោះបីជាអន្តរកម្មរវាងអាតូមនៅក្នុងសម្ភារៈត្រូវបានដោះស្រាយនៅមាត្រដ្ឋានម៉ាក្រូស្កូបក៏ដោយ។ វិធីសាស្រ្តធម្មតារួមមានដែនពេលវេលាភាពខុសគ្នាកំណត់បីវិមាត្រ (3D FDTD) និងការពង្រីក eigenmode (EME)។ វិធីសាស្រ្តទាំងនេះគឺត្រឹមត្រូវបំផុត ប៉ុន្តែមិនមានប្រសិទ្ធភាពសម្រាប់ពេលវេលាក្លែងធ្វើ PIC ទាំងមូល។ កម្រិតបន្ទាប់គឺការក្លែងធ្វើ EM 2.5 វិមាត្រ ដូចជាការសាយភាយធ្នឹមភាពខុសគ្នាកំណត់ (FD-BPM)។ វិធីសាស្រ្តទាំងនេះលឿនជាង ប៉ុន្តែលះបង់ភាពត្រឹមត្រូវខ្លះ ហើយអាចដោះស្រាយបានតែការសាយភាយ paraxial ប៉ុណ្ណោះ ហើយមិនអាចប្រើដើម្បីក្លែងធ្វើឧបករណ៍រំញ័របានទេ។ កម្រិតបន្ទាប់គឺការក្លែងធ្វើ EM 2D ដូចជា 2D FDTD និង 2D BPM។ ទាំងនេះក៏លឿនជាងដែរ ប៉ុន្តែមានមុខងារមានកំណត់ ដូចជាពួកវាមិនអាចក្លែងធ្វើឧបករណ៍បង្វិលប៉ូឡារីសេសិនបានទេ។ កម្រិតមួយទៀតគឺការក្លែងធ្វើម៉ាទ្រីសបញ្ជូន និង/ឬការខ្ចាត់ខ្ចាយ។ សមាសធាតុសំខាន់ៗនីមួយៗត្រូវបានកាត់បន្ថយទៅជាសមាសធាតុដែលមានការបញ្ចូល និងទិន្នផល ហើយមគ្គុទ្ទេសក៍រលកដែលបានភ្ជាប់ត្រូវបានកាត់បន្ថយទៅជាធាតុផ្លាស់ប្តូរដំណាក់កាល និងធាតុចុះខ្សោយ។ ការក្លែងធ្វើទាំងនេះមានល្បឿនលឿនបំផុត។ សញ្ញាទិន្នផលត្រូវបានទទួលដោយការគុណម៉ាទ្រីសបញ្ជូនដោយសញ្ញាបញ្ចូល។ ម៉ាទ្រីសខ្ចាត់ខ្ចាយ (ធាតុរបស់វាត្រូវបានគេហៅថាប៉ារ៉ាម៉ែត្រ S) គុណសញ្ញាបញ្ចូល និងទិន្នផលនៅម្ខាងដើម្បីស្វែងរកសញ្ញាបញ្ចូល និងទិន្នផលនៅម្ខាងទៀតនៃសមាសធាតុ។ ជាទូទៅ ម៉ាទ្រីសខ្ចាត់ខ្ចាយមានការឆ្លុះបញ្ចាំងនៅខាងក្នុងធាតុ។ ម៉ាទ្រីសខ្ចាត់ខ្ចាយជាធម្មតាមានទំហំធំជាងម៉ាទ្រីសបញ្ជូនពីរដងនៅក្នុងវិមាត្រនីមួយៗ។ សរុបមក ពីការក្លែងធ្វើ EM 3D ដល់ការក្លែងធ្វើម៉ាទ្រីសបញ្ជូន/ខ្ចាត់ខ្ចាយ ស្រទាប់នីមួយៗនៃការក្លែងធ្វើបង្ហាញពីការដោះដូររវាងល្បឿន និងភាពត្រឹមត្រូវ ហើយអ្នករចនាជ្រើសរើសកម្រិតត្រឹមត្រូវនៃការក្លែងធ្វើសម្រាប់តម្រូវការជាក់លាក់របស់ពួកគេ ដើម្បីបង្កើនប្រសិទ្ធភាពដំណើរការផ្ទៀងផ្ទាត់ការរចនា។

ទោះជាយ៉ាងណាក៏ដោយ ការពឹងផ្អែកលើការក្លែងធ្វើអេឡិចត្រូម៉ាញ៉េទិចនៃធាតុមួយចំនួន និងការប្រើប្រាស់ម៉ាទ្រីសខ្ចាត់ខ្ចាយ/ផ្ទេរដើម្បីក្លែងធ្វើ PIC ទាំងមូលមិនធានានូវការរចនាត្រឹមត្រូវទាំងស្រុងនៅពីមុខបន្ទះលំហូរនោះទេ។ ឧទាហរណ៍ ប្រវែងផ្លូវដែលបានគណនាខុស រលកមគ្គុទ្ទេសក៍ពហុរបៀបដែលបរាជ័យក្នុងការទប់ស្កាត់របៀបលំដាប់ខ្ពស់ប្រកបដោយប្រសិទ្ធភាព ឬរលកមគ្គុទ្ទេសក៍ពីរដែលនៅជិតគ្នាពេក ដែលនាំឱ្យមានបញ្ហាភ្ជាប់ដែលមិននឹកស្មានដល់ ទំនងជាមិនត្រូវបានរកឃើញក្នុងអំឡុងពេលក្លែងធ្វើ។ ដូច្នេះ ទោះបីជាឧបករណ៍ក្លែងធ្វើកម្រិតខ្ពស់ផ្តល់នូវសមត្ថភាពផ្ទៀងផ្ទាត់ការរចនាដ៏មានឥទ្ធិពលក៏ដោយ វានៅតែត្រូវការការប្រុងប្រយ័ត្នខ្ពស់ និងការត្រួតពិនិត្យយ៉ាងប្រុងប្រយ័ត្នដោយអ្នករចនា រួមផ្សំជាមួយនឹងបទពិសោធន៍ជាក់ស្តែង និងចំណេះដឹងបច្ចេកទេស ដើម្បីធានាបាននូវភាពត្រឹមត្រូវ និងភាពជឿជាក់នៃការរចនា និងកាត់បន្ថយហានិភ័យនៃសន្លឹកលំហូរ។

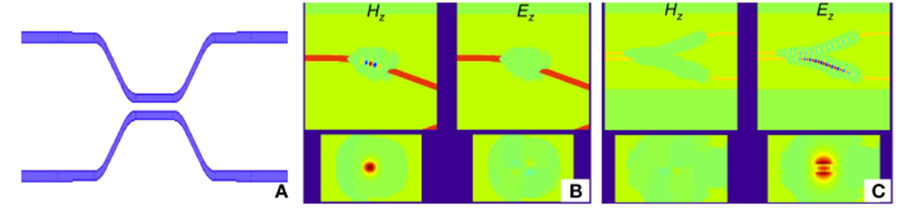

បច្ចេកទេសមួយហៅថា sparse FDTD អនុញ្ញាតឱ្យការក្លែងធ្វើ FDTD 3D និង 2D ត្រូវបានអនុវត្តដោយផ្ទាល់លើការរចនា PIC ពេញលេញដើម្បីផ្ទៀងផ្ទាត់ការរចនា។ ទោះបីជាវាពិបាកសម្រាប់ឧបករណ៍ក្លែងធ្វើអេឡិចត្រូម៉ាញ៉េទិចណាមួយក្នុងការក្លែងធ្វើ PIC ទ្រង់ទ្រាយធំក៏ដោយ sparse FDTD អាចក្លែងធ្វើតំបន់ក្នុងស្រុកដ៏ធំមួយ។ នៅក្នុង 3D FDTD បែបប្រពៃណី ការក្លែងធ្វើចាប់ផ្តើមដោយការចាប់ផ្តើមសមាសធាតុទាំងប្រាំមួយនៃដែនអេឡិចត្រូម៉ាញ៉េទិចនៅក្នុងបរិមាណជាក់លាក់មួយ។ នៅពេលដែលពេលវេលារីកចម្រើន សមាសធាតុដែនថ្មីនៅក្នុងបរិមាណត្រូវបានគណនា ហើយដូច្នេះនៅលើ។ ជំហាននីមួយៗតម្រូវឱ្យមានការគណនាច្រើន ដូច្នេះវាត្រូវការពេលយូរ។ នៅក្នុង sparse 3D FDTD ជំនួសឱ្យការគណនានៅជំហាននីមួយៗនៅចំណុចនីមួយៗនៃបរិមាណ បញ្ជីនៃសមាសធាតុដែនត្រូវបានរក្សាទុកដែលអាចត្រូវគ្នានឹងទ្រឹស្តីទៅនឹងបរិមាណធំតាមអំពើចិត្ត និងត្រូវបានគណនាសម្រាប់តែសមាសធាតុទាំងនោះប៉ុណ្ណោះ។ នៅជំហានពេលវេលានីមួយៗ ចំណុចដែលនៅជាប់នឹងសមាសធាតុដែនត្រូវបានបន្ថែម ខណៈពេលដែលសមាសធាតុដែននៅក្រោមកម្រិតថាមពលជាក់លាក់មួយត្រូវបានទម្លាក់ចុះ។ សម្រាប់រចនាសម្ព័ន្ធមួយចំនួន ការគណនានេះអាចលឿនជាង FDTD 3D បែបប្រពៃណីជាច្រើនលំដាប់។ ទោះជាយ៉ាងណាក៏ដោយ FDTDS ដ៏កម្រមិនដំណើរការល្អនៅពេលដោះស្រាយជាមួយរចនាសម្ព័ន្ធបំបែកទេ ពីព្រោះវាលពេលវេលានេះរីករាលដាលច្រើនពេក ដែលបណ្តាលឱ្យមានបញ្ជីដែលវែងពេក និងពិបាកគ្រប់គ្រង។ រូបភាពទី 1 បង្ហាញឧទាហរណ៍រូបថតអេក្រង់នៃការក្លែងធ្វើ FDTD 3D ស្រដៀងនឹងឧបករណ៍បំបែកធ្នឹមប៉ូឡារីសាស្យុង (PBS)។

រូបភាពទី 1: លទ្ធផលនៃការក្លែងធ្វើពី 3D sparse FDTD។ (ក) គឺជាទិដ្ឋភាពពីលើនៃរចនាសម្ព័ន្ធដែលកំពុងក្លែងធ្វើ ដែលជាឧបករណ៍ភ្ជាប់ទិសដៅ។ (ខ) បង្ហាញរូបថតអេក្រង់នៃការក្លែងធ្វើដោយប្រើការរំញោច quasi-TE។ ដ្យាក្រាមពីរខាងលើបង្ហាញទិដ្ឋភាពពីលើនៃសញ្ញា quasi-TE និង quasi-TM ហើយដ្យាក្រាមពីរខាងក្រោមបង្ហាញទិដ្ឋភាពឆ្លងកាត់ដែលត្រូវគ្នា។ (គ) បង្ហាញរូបថតអេក្រង់នៃការក្លែងធ្វើដោយប្រើការរំញោច quasi-TM។

ពេលវេលាបង្ហោះ៖ ថ្ងៃទី ២៣ ខែកក្កដា ឆ្នាំ ២០២៤